# **PowerPC 405GP**

# **Reference Design Kit**

# **User's Manual**

Version 0.8

**PRELIMINARY VERSION**

#### SecondEdition (August 2000)

This edition of the IBM PowerPC 405GP Reference Design Kit User's Manual applies to the IBM PowerPC 405GP Reference Design Kit and to all subsequent versions of the PowerPC 405GP Reference Design Kit until otherwise indicated in new versions or technical newsletters.

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS DOCUMENT "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions; therefore, this statement may not apply to you. IBM does not warrant that the use of the information herein shall be free from third party intellectual property claims.

IBM does not warrant that the contents of this document will meet your requirements or that the document is error-free. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the document. IBM may make improvements and or changes in the product(s) and/or program(s) described in this document at any time. This document does not imply a commitment by IBM to supply or make generally available the product(s) described herein.

The products described in this document are not intended for use in implantation or other direct life support applications.

All performance data contained in this document was obtained in a specific environment, and is presented as an illustration. The results obtained in other operating environments may vary.

No part of this document may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the written permission of IBM.

Address comments about this document to:

IBM Corporation Department YM5A P.O. Box 12195 Research Triangle Park, NC 27709

email: ppcsupp@us.ibm.com

IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

IBM may have patents or pending patent applications covering the subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Licensing, 500 Columbus Avenue, Thornwood, NY 10594, United States of America.

©Copyright International Business Machines Corporation 1999. All rights reserved.

Printed in the United States of America.

Notice to U.S. Government Users – Documentation Related to Restricted Rights – Use, duplication, or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corporation.

The following terms are trademarks of IBM Corporation: IBM OS Open AIX AIXwindows PPC405GP RISC System/6000 PowerPC PowerPC PowerPC Architecture RISCWatch RISCTrace Other terms which are trademarks are the property of their respective owners.

# Contents

| Figures                                               | ix    |

|-------------------------------------------------------|-------|

| Tables                                                | xi    |

| About This Book                                       | xiii  |

| Overview of the Reference Design Kit                  | . 1-1 |

| Hardware Components                                   | . 1-1 |

| Reference Platform                                    | . 1-1 |

| Cables and Power Supply                               | . 1-1 |

| Software Components                                   | . 1-1 |

| BSP Software                                          | . 1-1 |

| ROM Monitor                                           | . 1-2 |

| OS Open Real-Time Operating System                    | . 1-2 |

| Dhrystone Benchmark Program                           | . 1-2 |

| Application Tools                                     | . 1-2 |

| RISCWatch Debugger                                    | . 1-3 |

| IBM High C/C++ Evaluation Compiler                    | . 1-3 |

| Host System Requirements                              | . 2-1 |

| PC Host System Requirements                           | . 2-1 |

| SUN Host System Requirements                          | . 2-2 |

| RS/6000 Host System Requirements                      | . 2-2 |

| Installing the Software                               | . 3-1 |

| PC Software Installation                              | . 3-1 |

| BSP Software Installation - PC                        |       |

| High C/C++ Evaluation Compiler Installation - PC      | . 3-2 |

| RISCWatch Debugger Installation - PC                  |       |

| Sun Software Installation                             |       |

| BSP Software Installation - Sun                       | . 3-3 |

| High C/C++ Evaluation Compiler Installation - Sun     |       |

| RISCWatch Debugger Installation - Sun                 |       |

| RS/6000 Software Installation                         | . 3-7 |

| BSP Software Installation - RS/6000                   | . 3-7 |

| HIgh C/C++ Evaluation Compiler Installation - RS/6000 |       |

| RISCWatch Debugger Installation - RS/6000             | 3-10  |

| Host Configuration                                    | . 4-1 |

| PC Host Configuration                                 | . 4-1 |

| Serial Port Setup - PC                                |       |

| Ethernet Setup - PC                                   |       |

| ROM Monitor-Debugger Communication Setup - PC         |       |

| Sun Host Configuration                                | . 4-3 |

| Serial Port Setup - SUN                               |       |

| Ethernet Setup - SUN                                  |       |

| ROM Monitor-Debugger Communication Setup - SUN        |       |

| RS/6000 Host Configuration                            |       |

| Serial Port Setup - RS/6000                           |       |

| Ethernet Setup - RS/6000                              |       |

| ROM Monitor-Debugger Communication Setup - RS/6000    |       |

| Hardware                                              |       |

| Board Connectors                                      |       |

| Connecting the Reference Board to the Host            |       |

| Using a Terminal Emulator                             | . 6-3 |

| PC Terminal Emulation                                           | . 6-3 |

|-----------------------------------------------------------------|-------|

| SUN Terminal Emulation                                          | . 6-4 |

| RS/6000 Terminal Emulation                                      | . 6-5 |

| Board Reset                                                     | . 6-6 |

| ROM Monitor                                                     | . 7-1 |

| ROM Monitor Source Code                                         | . 7-1 |

| Communications Features                                         | . 7-2 |

| Configuration of bootp and tftp to Support ROM Monitor Loads    | . 7-2 |

| PC bootp and tftp Configuration                                 | . 7-2 |

| SUN bootp and tftp Configuration                                | . 7-4 |

| RS/6000 bootp and tftp Configuration                            | . 7-5 |

| Accessing the ROM Monitor                                       | . 7-6 |

| ROM Monitor Operation                                           | . 7-6 |

| Monitor Selections and Submenus                                 | . 7-7 |

| Initial ROM Monitor Menu                                        | . 7-8 |

| Selecting Power-On Tests                                        | . 7-9 |

| Selecting Boot Devices                                          | 7-10  |

| Changing IP Addresses                                           |       |

| Using the Ping Test                                             |       |

| Entering the Debugger                                           |       |

| Disabling the Automatic Display                                 |       |

| Displaying the Current Configuration                            |       |

| Saving the Current Configuration                                |       |

| Setting the Baud Rate for S1 Boots                              |       |

| S1 Boot                                                         |       |

| Exiting the Main Menu                                           |       |

| Cache Options                                                   |       |

| ROM Monitor User Functions                                      |       |

| Flash Update Utility                                            |       |

| Network Address of the Ethernet Controller                      |       |

| Sample Applications                                             |       |

| Overview                                                        |       |

| ROM Monitor Flash Image                                         |       |

| Using the Software Samples                                      |       |

| Building and Running the Dhrystone Benchmark                    |       |

| Building and Running the usr_samp Program                       |       |

| Building and Running the timesamp Program                       |       |

| Setting the time in the on-board clock                          |       |

| PPC405 MAC instruction sample                                   |       |

| Resolving Execution Problems                                    |       |

| Using the Ping Test on the ROM Monitor to Verify Connectivity   |       |

| Setup of bootp and tftp Servers (Daemons) for ROM Monitor Loads |       |

| Using OS Open Functions                                         |       |

| Application Libraries and Tools                                 |       |

| OS Open Libraries                                               |       |

| Using Libraries and Support Software                            |       |

| Serial Port Support Library                                     |       |

| Boot Library (RAM)                                              |       |

| Input/Output Support Library                                    |       |

| Keyboard/Mouse Controller Support Library                       |       |

| I2C Library                                                     |       |

| PowerPC Low-Level Processor Access Support Library              |       |

| ROM Monitor Ethernet IP Interface Library                       |       |

| Real-time Clock Interface Support Library                       |       |

|                                                                 | 3-0   |

| Ethernet Device Driver Support Library                  | . 9-5 |

|---------------------------------------------------------|-------|

| Software Timer Tick Support Library                     | . 9-5 |

| Device Drivers Supplied with the Board Support Software | . 9-5 |

| Asynchronous Device Driver                              |       |

| Device Driver Installation                              | . 9-6 |

| Device Installation                                     |       |

| Opening Asynchronous Communication Ports                |       |

| Reading and Writing                                     | . 9-8 |

| I/O Control                                             | . 9-9 |

| Polled Asynchronous I/O                                 | 9-10  |

| Flow control                                            |       |

| Keyboard/Mouse Controller Driver                        | 9-11  |

| Device Driver Installation                              | 9-11  |

| Device Installation                                     | 9-12  |

| Opening Keyboard Port                                   | 9-12  |

| Reading                                                 | 9-13  |

| I/O Controls                                            | 9-13  |

| Translation Function                                    | 9-14  |

| I2C Device Driver                                       | 9-15  |

| Functional Description                                  | 9-15  |

| I2C Initialisation                                      | 9-15  |

| I2C read                                                | 9-15  |

| I2C write                                               | 9-16  |

| Accessing I2C Registers                                 | 9-16  |

| VGA Support                                             | 9-16  |

| VGA Card Initialisation                                 | 9-17  |

| Common Functions                                        | 9-17  |

| Text mode                                               | 9-17  |

| Graphics Modes                                          | 9-19  |

| VGA registers                                           | 9-19  |

| VGA device driver                                       | 9-20  |

| VGA sample                                              | 9-21  |

| Ethernet Device Driver                                  |       |

| Device Driver Installation                              | 9-22  |

| Device Installation                                     |       |

| Opening and Closing Ethernet Files                      | 9-23  |

| Reading and Writing                                     |       |

| I/O Control                                             |       |

| ENET_SET_CHANNEL                                        | 9-24  |

| ENET_CLEAR_CHANNEL                                      |       |

| ENET_QUERY_ADDRESS                                      |       |

| MIB Functions                                           |       |

| ROM Monitor Ethernet Device Driver                      |       |

| Environment Startup and Initialization                  |       |

| Board Bootstrap                                         |       |

| Environment Initialization                              | 9-26  |

| Tools                                                   | -     |

| elf2rom                                                 |       |

| hbranch                                                 |       |

| eimgbld                                                 |       |

| OS Open Function Reference                              |       |

| Attributes and Threads                                  |       |

| Async Safe Functions                                    |       |

| Cancel Safe Functions                                   | 10-1  |

| Interrupt Handler Safe Functions                 | 10-1  |

|--------------------------------------------------|-------|

| Callable from Application Thread Group Functions |       |

| Functions                                        |       |

| Program Trace Calls                              |       |

| Overview                                         |       |

| MSGDATA Structure                                |       |

| Ptrace Definitions                               |       |

| RD_ATTACH (30)                                   |       |

|                                                  |       |

| RD_DETACH (31)                                   |       |

| RD_FILL (105)                                    |       |

| RD_KILL (8)                                      |       |

| RD_LDINFÓ (34)                                   |       |

| RD_LOAD (101)                                    |       |

| RD_LOGIN (103)                                   |       |

| RD_LOGOFF (104)                                  |       |

| RD_READ_D (2)                                    |       |

| RD_READ_FPR (12)                                 |       |

| RD_READ_GPR (11)                                 |       |

| RD_READ_GPR_MULT(71)                             |       |

| RD_READ_I (1)                                    |       |

| RD_READ_I_MULT (71)                              |       |

| RD_READ_SPR (115)                                |       |

| RD_READ_SR (118)                                 |       |

| RD_STATUS (114)                                  |       |

| RD_STOP_APPL (113)                               |       |

| RD_WAIT (108)                                    |       |

| RD_WRITE_BLOCK (19)                              |       |

| RD_WRITE_D (5)                                   |       |

| RD_WRITE_FPR (15)                                | A-28  |

| RD_WRITE_GPR (14)                                | A-29  |

| RD_WRITE_I (4)                                   | A-30  |

| RD_WRITE_SPR (112)                               | A-31  |

| RD_WRITE_SR (119)                                | A-32  |

| RL_LDINFO (181)                                  | A-33  |

| RL_LOAD_REQ(180)                                 |       |

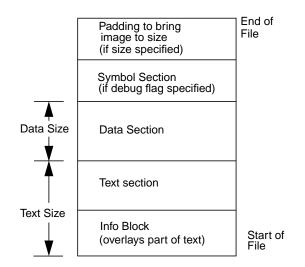

| ROM Monitor Load Format                          |       |

| Overview                                         | . B-1 |

| Section Types                                    |       |

| First Section                                    | . B-2 |

| Text Section                                     |       |

| Data Section                                     |       |

| Symbol Section                                   |       |

| Boot Header                                      | . B-3 |

# Figures

| Serial Port Connection             | 6-1  |

|------------------------------------|------|

| Point-to-Point Ethernet Connection | 6-2  |

| Wiring in a Crossover Cable        | 6-2  |

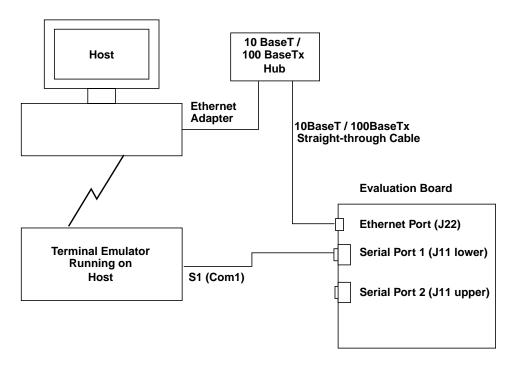

| Ethernet Connection with Hub       |      |

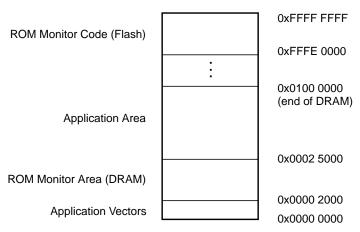

| ROM Monitor Address Map            | 7-7  |

| elf2rom Output File                |      |

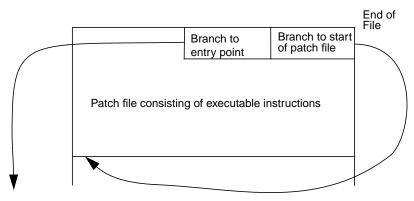

| Detail of Patch File Placement     |      |

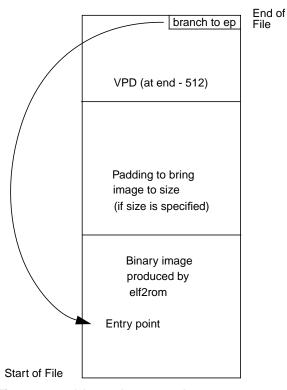

| hbranch Output Image               | 9-30 |

# Tables

| OS Open Libraries                                  | 9-1  |

|----------------------------------------------------|------|

| OS Open Libraries for the Reference Board Platform |      |

| Additional Parameters Passed to driver_install()   | 9-7  |

| Additional Parameters Passed to open()             | 9-8  |

| ioctl() Commands for Asynchronous Device Drivers   | 9-9  |

| Additional Parameters Passed to driver_install()   | }-12 |

| Functions Specific to the PPC405GP Design Kit 1    | 0-2  |

# **About This Book**

This book contains the information you need to install and use the IBM® PowerPC 405GP Reference Design Kit, a hardware and software development tool for the PowerPC PPC405GP 32-bit RISC microprocessor.

The PowerPC 405GP Reference Design Kit (hereinafter referred to as the PPC405GP design kit) hardware includes the PowerPC 405 Reference Board (hereinafter referred to as the reference board), power supply, and board interface cables. The board and power supply are housed in an ATX form factor case. Features of the reference board include a PowerPC PPC405GP processor, 16MB SDRAM, four 32-bit PCI slots, built-in Ethernet support, 512KB socketed flash memory, 512KB SRAM, 2 serial ports, a time-of-day clock with 8KB NVRAM, an IR controller, and a mouse/keyboard controller.

The PPC405GP design kit software includes the ROM Monitor (resident in the flash memory on the board), ROM Monitor source code, IBM's OS Open real time operating system, sample application programs, application development libraries and tools, IBM's High C/C++ compiler, and IBM's RISCWatch, a source-level debugger that runs on the host system.

The PPC405GP design kit also includes technical specifications and board schematics.

Connection of the reference board to a host system is required for the exercises in this book. Supported host systems include:

- An IBM or compatible PC running one of the following:

- Windows 95/98

- Windows NT 4.0

- A Sun SPARCstation 5, 10, or 20 workstation running one of the following:

- Solaris 2.4 (or higher)

- SunOS 4.1.3 (or higher)

- An IBM RISC System/6000<sup>™</sup> workstation running AIX<sup>™</sup> 4.1 (or higher)

## Who Should Use This Book

This book is for hardware and software developers who need to evaluate the PowerPC PPC405GP microprocessor and use the debugging features of the PowerPC 405GP Reference Design Kit to support software development.

Users should understand hardware and software development tools, concepts, and environments. Specifically, users should understand:

- The host's operating system

- The PowerPC Architecture<sup>™</sup> and implementation-specific characteristics of the PowerPC microprocessor being used

- C and Assembler language programming

## How to Use This Book

This book contains the following chapters and appendixes:

Chapter 1, "Overview of the Reference Design Kit" describes the product, its hardware and software components, and its relationship with the software tools on the host.

Chapter 2, "Host System Requirements" lists the hardware and software requirements of the host system.

Chapter 3, "Installing the Software" describes the software installation on the host system.

Chapter 4, "Host Configuration" describes the steps required to facilitate communications between the host computer and the reference board.

Chapter 5, "Hardware" describes the reference board, its memory map, its hardware components and their functions.

Chapter 6, "Board Connectors" describes the reference board connectors and the procedures for connecting the board to a host system.

Chapter 7, "ROM Monitor" describes the operations of the ROM monitor.

Chapter 8, "Sample Applications" describes how to compile, load, and run the sample applications on the reference board.

Chapter 9, "Application Libraries and Tools" describes the application libraries and host tools provided with the reference board software.

Chapter 10, "OS Open Function Reference" lists the OS Open functions for the PowerPC 405 Reference Board platform. The function calls are arranged alphabetically by function name.

Appendix A, "Program Trace Calls" describes the messages for interfacing a debugger on the host system to the ROM Monitor on the reference board.

Appendix B, "ROM Monitor Load Format" describes the load format requirements supported by the ROM monitor.

## **Conventions Used in This Book**

This book follows the numeric and highlighting notation conventions based on those used in the RISC System/6000 and AIX publications.

#### **Numeric Conventions**

In general, numbers are used exactly as shown. Unless noted otherwise, all numbers are in decimal, and, if entered as part of a command, are entered without format information.

In text, binary numbers are preceded by a "B" followed by the number enclosed in single quotes, for example:

B'010'

In commands, binary numbers are preceded by "0b" or "b" followed by the number, which may be enclosed in single quotes, for example:

0b010 or b'010'

In text, hexadecimal numbers are preceded by an "X" followed by the number enclosed in single quotes, for example:

X'1A7'

In commands, hexadecimal numbers are preceded by "0x" or "x" followed by the number, which may be enclosed in single quotes, for example:

0x1a7 or x'1a7'

In text, the hexadecimal digits A through F appear in uppercase. In commands, these digits are typically entered in lowercase.

## **Highlighting Conventions**

This book uses the following highlighting conventions:

The names of invariant objects known to the software appear in bold type. In some text, however, such as in lists, no special typographic treatment is used. Examples of such objects include:

- Function and macro names

- Data types and structures

- Constants and flags

Names of objects known to the software must be entered exactly as shown.

- Variable names supplied by user programs appear in italic type. In some text, however, such as in lists, no special typographic treatment is used. Examples of these objects include arguments and other parameters.

- No highlighting appears in code examples.

## **Syntax Diagram Conventions**

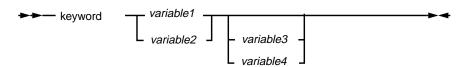

Throughout this book, diagrams illustrate the syntax for string formats and commands. The following list shows how to read these diagrams:

- Read the syntax diagrams from left to right, from top to bottom, following the path of the line.

- A ►► symbol begins a diagram.

- A ----- symbol indicates continuation of a diagram on the next line.

- A symbol indicates continuation of a diagram from the previous line.

- A For symbol terminates a diagram.

- Keywords are in regular type, and variables are in italics. Keywords must be typed exactly as shown.

- Keywords or variables on the main path of a diagram are required.

►► keyword — variable1 — variable2 –

• Keywords or variables shown on branches below the main path are optional.

►► keyword

variable1

• Keywords or variables can appear in a stack, indicating that only one item in a stack can be chosen. If an item in a stack is on the main path, you must choose an item from the stack. If all items in a stack are below the main path, you may choose an item from the stack.

For example, in the following syntax diagram, you must choose either *variable1* or *variable2*. However, because *variable3* and *variable4* are below the main path, neither is required.

• A repeat separator is a returning arrow that surrounds a syntax element or group and shows that the element or group can be repeated.

## Contacting the IBM Embedded Systems Solution Center

For information about the PowerPC 405GP Reference Design Kit and the IBM family of hardware and software products for embedded system developers, call the IBM Embedded Systems Solution Center at (919) 543-5701, or check out the IBM Microelectronics web site at:

http://www.chips.ibm.com/products/embedded

Please send any comments or questions regarding this product to the following Internet address:

ppcsupp@us.ibm.com

#### **Related Publications**

Many of the following publications are included on the CD ROM that comes with the evaluation kit. The others are available from your IBM Microelectronics representative:

• Embedded Application Binary Interface (EABI) Publications

PowerPC Embedded Application Binary Interface (EABI) System V Application Binary Interface, Third Edition, 0-13-0100439-5 System V Application Binary Interface, PowerPC Processor Supplement

• IBM High C/C++ Publications

The following list includes the books in the IBM High C/C++ library:

IBM High C/C++ Programmer's Guide for PowerPC, 92G6920 IBM High C/C++ Language Reference for PowerPC, 92G6923 IBM ELF Assembler User's Guide for PowerPC, 92G6921 IBM ELF Linker User's Guide for PowerPC, 92G6922

• OS Open Publications

IBM OS Open Programmer's Reference, Volume 1, 92G6911 IBM OS Open Programmer's Reference, Volume 2, 92G6912 IBM OS Open User's Guide, 92G6897

- RISCWatch Debugger Publications

- RISCWatch Debugger User's Guide, 13H6964 RISCWatch Debugger Installation Guide, 13H6984

- PowerPC PPC405GP User's Manual

PowerPC 405GP RISC Microprocessor User's Manual,

- Reference Board Publications

*PowerPC 405 Reference Board Manual*

## Chapter 1. Overview of the Reference Design Kit

This chapter introduces the hardware and software components included in the PPC405GP design kit.

## **1.1 Hardware Components**

The PPC405GP design kit contains the reference board, power supply line cord, serial port and Ethernet cables.

## 1.1.1 Reference Platform

The reference board and power supply are housed in an ATX form factor case. Features of the reference board include the PowerPC PPC405GP processor, 16MB SDRAM, four 32-bit PCI slots, built-in Ethernet support (10BaseT/100BaseTX), 512KB socketed flash memory, 512KB SRAM, 2 serial ports, a time-of-day clock with 8KB NVRAM, I<sup>2</sup>C port, IR port, and a mouse/keyboard controller. A PCI VGA display adapter is also included in the kit.

For a detailed description of the reference board, refer to the PowerPC 405 Reference Board Manual.

## 1.1.2 Cables and Power Supply

The PPC405GP design kit includes a serial port interface cable for connecting the board's serial port 1 to a terminal or terminal emulator running on the host. The Sun version of the kit also contains a male-to-male adapter to support this connection.

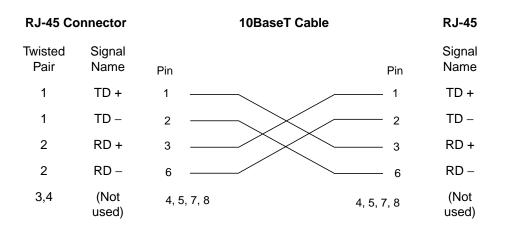

An Ethernet crossover cable is provided in the kit to support direct Ethernet communication with the host system. A standard 10BaseT/100BaseTX RJ45 Ethernet connector is provided on the reference board. The Ethernet crossover cable is for direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. The crossover cable is only supported for 10Mb/s operation - for 100Mb/s a hub (not supplied) should be used.

A power supply line cord is also provided with the PPC405GP design kit.

## **1.2 Software Components**

The PPC405GP design kit software consists of the Board Support Package (BSP), the RISCWatch source level debugger, and the IBM High C/C++ evaluation compiler.

## 1.2.1 BSP Software

The BSP software includes the ROM Monitor code resident in flash memory, ROM Monitor source code, the IBM OS Open real time operating system, several sample programs (including the Dhrystone benchmark program), and application development libraries and tools.

## 1.2.1.1 ROM Monitor

The ROM Monitor program for the reference board is supplied in the 512KB socketed flash memory module on the reference board. This code initializes the 405GP processor and the board for serial and Ethernet communications. By supporting communications with the host computer system, the ROM Monitor allows applications to be loaded from the host onto the board and debugged using the RISCWatch source level debugger in ROM Monitor mode.

The ROM Monitor is accessed through a terminal (or terminal emulator) attached to serial port 1 on the board. The RISCWatch debugger, when in ROM Monitor mode, runs on the host system, communicating with the ROM Monitor through serial port 2 or the Ethernet interface on the board.

The ROM Monitor source code is provided and can be readily used for product development. The availability of the code helps lower software development costs and quicken product time to market. The code is also provided so that debuggers other than RISCWatch may be integrated with the PPC405GP design kit. Appendix A describes the trace calls that support communication between the RISCWatch debugger on the host and the ROM Monitor running on the board.

## 1.2.1.2 OS Open Real-Time Operating System

OS Open is a real-time operating system (RTOS) available for the PowerPC 400, 600, and 700 families of processors. OS Open is designed to take full advantage of the power of the IBM PowerPC RISC processors. Also, because the OS Open environment is built in a scalable fashion, it can be configured to meet the functional requirements and memory constraints of a wide variety of embedded systems.

OS Open features:

- Hard real-time support, including deterministic execution, priority inheritance protocols, and priority ceiling protocols

- · Board support packages for plug-and-play operation of popular board-level products

- Support for existing American National Standards Institute (ANSI) C and emerging POSIX standards

- · Open network interfaces to support embedded systems in heterogeneous environments

- Scalable implementations to meet the requirements and constraints of a variety of embedded systems

The version of OS Open included in the BSP software contains a reduced-function kernel that limits the number of threads that can be in existence at one time. Additional details can be found in the README file following software installation. A full-function OS Open kernel is available from IBM. Contact the IBM Embedded Systems Solutions Center at (919) 543-5701 for additional information.

## 1.2.1.3 Dhrystone Benchmark Program

The Dhrystone benchmark is a commonly available integer benchmark. It is included as an example program to be built, loaded onto the board, and executed. The results of this benchmark may vary based on compiler options and the system environment in which it is run.

## 1.2.1.4 Application Tools

Several host-based tools are provided to support ROM and application development on the reference board.

## 1.2.2 RISCWatch Debugger

The RISCWatch source level debugger provides a window-based debugging environment for loading, debugging, and executing application programs on the board. Debugger installation and usage for ROM Monitor and OS Open (non-JTAG) targets are addressed in the *RISCWatch Debugger Installation Guide* and the *RISCWatch Debugger User's Guide* included on the publications CD-ROM in the kit. A sample debug session is included with the debugger.

## 1.2.3 IBM High C/C++ Evaluation Compiler

The IBM High C/C++ compiler is a globally optimizing compiler developed for the PowerPC family of processors. It produces executable code in Extended Link Format (ELF) file format. The version included in the kit is a limited capacity version created specifically for the PPC405GP design kit. It supports the compilation, assembly, and linkage of the sample application programs and the ROM Monitor source code. A full featured version of the IBM High C/C++ compiler is available from IBM. For more information call the PowerPC Embedded Systems Solutions Center at (919) 543-5701.

## Chapter 2. Host System Requirements

This chapter describes the hardware and software requirements of the host system to which the reference board is to be connected. Supported host systems include:

- IBM (or compatible) PC running one of the following:

- Windows 95/98

- Windows NT 4.0

- Sun SPARCstation 5, 10, or 20 workstation running one of the following:

- Solaris 2.4 (or higher)

- SunOS 4.1.3 (or higher)

- IBM RS/6000 workstation running AIX 4.1 (or higher)

## 2.1 PC Host System Requirements

Hardware requirements of the host PC include:

- IBM or compatible system unit. Minimum requirements: x486 DX2 50/66MHz with 8MB of RAM

- VGA/SVGA Display Monitor. Minimum requirement: VGA 640 x 480. Recommended: SVGA 1024 x 768

- Approximately 30MB of free disk space. This space is required for the IBM High C/C++ compiler, the Board Support Package software, and the RISCWatch debugger. When planning disk space usage, consider disk space requirements for Windows and any other software packages.

- At least one available serial port for terminal emulation. A second serial port is required if a SLIP host-to-board connection is to be used instead of an Ethernet connection. For performance reasons, an Ethernet connection is strongly recommended. Establishing an Ethernet host-to-board connection will most likely require the installation of an Ethernet adapter card on the host (if not already installed) and some additional connectivity hardware. That hardware might include any or all of the following:

- An Ethernet 10BaseT/100BaseTX network transceiver, a twisted pair cable, and a hub. At a minimum, a point-to-point connection will require the Ethernet crossover cable supplied with the kit. The Ethernet crossover cable is for direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. The crossover cable is only supported for 10Mb/s operation for 100Mb/s a hub (not supplied) should be used.

The following software must be installed on the host PC to run the debugger that communicates with the ROM Monitor on the board:

- RISCWatch 4.0 or higher

- Windows 95/98 or Windows NT 4.0

Windows users who want to establish a SLIP host-to-board connection over a second serial port, require additional software since the TCP/IP package that comes with Windows does not support SLIP communications. One TCP/IP package that can be used for Windows SLIP communications is Trumpet Winsock, a TCP/IP protocol stack available from the www.trumpet.com Internet site.

Appropriate installation documentation can be found at the Trumpet site. Users should refer to the documentation for the terms and conditions of using Trumpet Winsock. Information regarding the setup and use of Trumpet Winsock can be found in Chapter 4, "Host Configuration."

**Note:** Trumpet is not recommended for Windows users already connected to a network since installing Trumpet may cause problems with previously defined networks. If the recommended Ethernet host-to-board connection is going to be used (instead of the SLIP host-to-board connection), Windows users need not install Trumpet since the TCP/IP package that comes with Windows can be used to establish the Ethernet connection.

## 2.2 SUN Host System Requirements

Hardware requirements of the host Sun workstation include:

- Approximately 30MB of free disk space. This space is required for the IBM High C/C++ compiler, the Board Support Package software, and the RISCWatch debugger. When planning disk space usage, consider disk space requirements for the operating system and any other software packages.

- An available serial port for terminal emulation and an Ethernet Attachment Unit Interface (AUI) or RJ-45 port for host-to-board communications. Most Sun SPARCstations come equipped with one serial port and an Ethernet AUI port. Consult your Sun literature for additional details.

- Any or all of the following hardware to establish an Ethernet connection between the board and the host.

- An Ethernet 10BaseT/100BaseTX network transceiver, a twisted pair cable, and a hub. At a minimum, a point-to-point connection will require the Ethernet crossover cable supplied with the kit. The Ethernet crossover cable is for direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. The crossover cable is only supported for 10Mb/s operation for 100Mb/s a hub (not supplied) should be used.

- A graphics display to display debugger screens

The following software must be installed on the Sun workstation to run the debugger that communicates with the ROM Monitor on the board:

- RISCWatch 4.0 or higher

- SunOS 4.1.3 (or higher) or Solaris 2.4 (or higher)

- A window system such as Open Windows or CDE

- Motif 1.2 (Solaris)

## 2.3 RS/6000 Host System Requirements

Hardware requirements of the host RS/6000 computer include:

• Approximately 30MB of free disk space. This space is required for the IBM High C/C++ compiler, the Board Support Package software, and the RISCWatch debugger. When planning disk space usage, consider disk space requirements for the operating system and any other software packages.

- At least one available serial port for terminal emulation. A second serial port is required if a SLIP host-to-board connection is to be used instead of an Ethernet connection. For performance reasons, an Ethernet connection is strongly recommended. Most RS/6000 computers come equipped with two serial ports and an Ethernet adapter. Please consult your RS/6000 literature for more details. Establishing an Ethernet host-to-board connection may require additional connectivity hardware. That hardware might include any or all of the following:

- An Ethernet 10BaseT/100BaseTX network transceiver, a twisted pair cable, and a hub. At a minimum, a point-to-point connection will require the Ethernet crossover cable supplied with the kit. The Ethernet crossover cable is for direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. The crossover cable is only supported for 10Mb/s operation for 100Mb/s a hub (not supplied) should be used.

- At least one available serial port for terminal emulation. A second serial port is required if a SLIP host-to-board connection is to be used instead of an Ethernet connection. For performance reasons, an Ethernet connection is strongly recommended. Most RS/6000 computers come equipped with two serial ports and an Ethernet adapter. Please consult your RS/6000 literature for more details.

- A graphics display (IBM 6091 or similar), to display debugger screens

The following software must be installed on the host RS/6000 computer to run the debugger that communicates with the ROM Monitor on the board:

- RISCWatch 4.0 or higher

- AIX Version 4.1 or higher

- AIX/Windows<sup>™</sup> with X11R5 and Motif 1.2

## Chapter 3. Installing the Software

This chapter describes the procedures for installing the BSP software and the High C/C++ Compiler on the host system. Details of the software, its directories and their contents, are also given. Instructions for installing the RISCWatch Debugger software can be found in the *RISCWatch Debugger Installation Guide*. Please refer to the section corresponding to your host system.

## 3.1 PC Software Installation

## 3.1.1 BSP Software Installation - PC

Before beginning the installation, you must have:

- BSP for PC installation diskettes

- A PC running Windows 95/98 or Windows NT 4.0

The following procedure installs the BSP software:

Note: For Windows NT users, we recommend that you log on as administrator.

- 1. Insert the installation diskette labeled "BSP PC" and "1 of n" (n may vary) into diskette drive A:.

- 2. Select Start from the Windows task bar.

- 3. Select Run.

- 4. Type **a:setup** then press **Enter** to run the installation program.

- 5. Follow the installation program instructions.

If the default install directory is accepted, the BSP software is installed in the **\osopen** directory tree. The **\osopen** directory tree contains the files and tools that support OS Open application and ROM development. The **\osopen** subdirectories and their contents are as follows.

#### \bin

This directory contains several host based utilities used for application and ROM program development.

- elf2rom.exe creates a ROM image from an ELF executable file

- eimgbld.exe creates a ROM Monitor loadable image from an ELF executable file

- · hbranch.exe places an absolute branch in the last address of a ROM image

- rambuild.exe creates an assembler source file that contains the files found in a specified directory

- make.exe supports the use of makefiles when building application programs

- bootpd.exe bootp server to support ROM Monitor downloads

- tftpd.exe tftp server to support host-to-board file transfers

#### \examples

This directory contains example OS Open programs.

#### \m405\_evb

This directory contains the ROM Monitor and OS Open platform specific code for the reference board included in the kit.

- README.TXT contains the latest information regarding this release

- **\include** contains OS Open include files

- \Id contains dynamically loadable modules that can be run from OS Open's OpenShell

- **\lib** contains OS Open libraries

- \m4 contains assembler preprocessor include files

- \openbios contains the source code for the ROM Monitor (See Chapter 7, "ROM Monitor")

- \samples contains samples programs that can be compiled and run

Considerable effort goes into providing a quality product with consistent documentation. To insure that our customers have the advantage of the latest software features and updated information, **README.TXT** contains clarifications and additional information and should be considered essential reading.

#### **\COMMENT.USR** and **\COMMENT.DOC**

Please take the time to complete these user comment forms. Your feedback and suggestions will help us to improve our products and technical publications. FAX and e-mail instructions are included in each of the files.

## 3.1.2 High C/C++ Evaluation Compiler Installation - PC

Before beginning the installation, you must have:

- High C/C++ for PC installation diskettes

- A PC running Windows 95/98 or Windows NT 4.0

The following procedure installs the High C/C++ compiler:

Note: For Windows NT users, we recommend that you log on as administrator.

- 1. Insert the installation diskette labeled "High C/C++ PC" and "1 of *n*" (*n* may vary) into diskette drive A:

- 2. Select **Start** from the Windows task bar.

- 3. Select Run.

- 4. Type **a:setup** then press **Enter** to run the installation program.

- 5. Follow the installation program instructions.

If the default install directory is accepted, the IBM High C/C++ Compiler is installed in the **\highcppc** directory tree. The **\highcppc\bin** directory contains the files required for the IBM High C/C++ Compiler. Those files include:

- asppc.exe assembler for assembler language programs

- Idppc.exe ELF linker/binder to build applications to be run on the board

- hcppc.exe High C/C++ compiler for C programs

- arppc.exe ELF library archiver

The readme file under the **\highcppc** directory contains the latest information regarding the compiler and should be considered essential reading.

## 3.1.3 RISCWatch Debugger Installation - PC

Please refer to the *RISCWatch Debugger Installation Guide* for debugger installation instructions. Be sure to follow the instructions for PC installation.

## 3.2 Sun Software Installation

## 3.2.1 BSP Software Installation - Sun

The software support package is installed from diskettes on a Sun host system using the **cpio** and **tar** commands.

Before beginning the installation, you must have:

- BSP for Sun installation diskettes

- A Sun SPARCstation 5, 10, or 20 workstation running SunOS 4.1.3 (or higher) or Solaris 2.4 (or higher)

- Superuser privileges on the Sun system

The procedures required for installing the BSP software support package vary depending on the operating system being used. Please follow the instructions corresponding to your operating system.

#### Instructions for SunOS 4.1.3 (or higher) only:

- 1. Log in as root or use the su command to become the superuser

- 2. Open at least two windows for this procedure

- 3. Use the **cd** command to change to the **/usr** directory

- 4. Insert the installation diskette labeled "BSP Sun" and "1 of n" (n may vary) into the diskette drive

- 5. From the second window run the command:

```

cpio -ivB BSP_os4.tar.Z BSP.tar.Z < /dev/rfd0</pre>

```

where /dev/rfd0 is the name of your diskette device.

- 6. When the system prompts you for a new volume, move to the first window and type **eject** to eject the diskette. Insert the next diskette.

- 7. Move to the second window and type the name of the diskette drive (/dev/rfd0) to continue the process.

- 8. If prompted for more diskettes, repeat the previous two steps. When finished, type **eject** to remove the final diskette.

- 9. Return to the first window and verify that the following files are installed under the *lusr* directory:

BSP.tar.Z

BSP\_os4.tar.Z

10. Run the following commands to unpack and install the files (order is important):

zcat BSP.tar.Z | tar xvf -

zcat BSP\_os4.tar.Z | tar xvf -

Installation for SunOS is complete. The tar.Z files may be removed to recover space.

#### Instructions for Solaris 2.4 (or higher) only:

- 1. Log in as **root** or use the **su** command to become the superuser.

- 2. Open at least two windows for this procedure.

- 3. Use the **cd** command to change to the **/usr** directory.

- 4. Insert the installation diskette labeled "BSP Sun" and "1 of n" (n may vary) into the diskette drive.

- 5. From the first window type **volcheck**. This creates a file called **/vol/dev/rdiskette0/unlabeled** (the diskette device name).

If the system opens a message box saying the diskette format is unrecognized, ignore the message and cancel the message box. The name of the file created may be different on your system. You can use the **eject -q** command to see the actual name. The file name returned is the name that should be used in the subsequent steps.

6. From the second window run the command:

cpio -ivB BSP.tar.Z < /vol/dev/rdiskette0/unlabeled</pre>

where /vol/dev/rdiskette0/unlabeled is the name of your diskette device.

- 7. When the system prompts you for a new volume, move to the first window. Type **eject** if the system did not automatically eject the diskette. Insert the next diskette and type **volcheck**.

- 8. Move to the second window and type the name of the diskette drive (/vol/dev/rdiskette0/unlabeled) to continue the process.

- 9. If prompted for more diskettes, repeat the previous two steps. When finished, type **eject** to remove the final diskette.

10.Return to the first window and verify that the following file is installed under the **/usr** directory:

#### BSP.tar.Z

11.Run the following command to unpack and install the files:

zcat BSP.tar.Z | tar xvf -

Installation for Solaris is complete. The tar.Z file may be removed to recover space.

The BSP software is installed in the **/usr/osopen** directory tree. It may be necessary to change ownership of these directories, their subdirectories and their contents if other users require access to them.

The **/usr/osopen** directory tree contains the files and tools that support OS Open application and ROM development. The **/usr/osopen** subdirectories and their contents are as follows.

#### /bin

This directory contains several host based utilities used for application and ROM program development.

- elf2rom creates a ROM image from an ELF executable file

- eimgbld creates a ROM Monitor loadable image from an ELF executable file

- hbranch places an absolute branch in the last address of a ROM image

- rambuild creates an assembler source file that contains the files found in a specified directory

- bootpd bootp server to support ROM Monitor downloads

#### /examples

This directory contains example OS Open programs.

#### /m405\_evb

This directory contains the ROM Monitor and OS Open platform specific code for the reference board included in the kit.

- **README.TXT** contains the latest information regarding this release

- /include contains OS Open include files

- /Id contains dynamically loadable modules that can be run from OS Open's OpenShell

- /lib contains OS Open libraries

- /m4 contains assembler preprocessor include files

- /openbios contains the source code for the ROM Monitor (See Chapter 7, "ROM Monitor")

- /samples contains samples programs that can be compiled and run

Considerable effort goes into providing a quality product with consistent documentation. To insure that our customers have the advantage of the latest software features and updated information, **README.TXT** contains clarifications and additional information and should be considered essential reading.

#### /COMMENT.USR and /COMMENT.DOC

Please take the time to complete these user comment forms. Your feedback and suggestions will help us to improve our products and technical publications. FAX and e-mail instructions are included in each of the files.

## 3.2.2 High C/C++ Evaluation Compiler Installation - Sun

The compiler is installed from diskettes on a Sun host system using the **cpio** and **tar** commands.

Before beginning the installation, you must have:

- "High C/C++ for Sun" installation diskettes

- A Sun SPARCstation 5, 10, or 20 workstation running SunOS 4.1.3 (or higher) or Solaris 2.4 (or higher)

- Superuser privileges on the Sun system

The procedures required for installing the High C/C++ compiler vary depending on the operating system being used. Please follow the instructions corresponding to your operating system.

#### Instructions for SunOS 4.1.3 (or higher) only:

- 1. Log in as root or use the su command to become the superuser.

- 2. Open at least two windows for this procedure.

- 3. Use the **cd** command to change to the **/usr** directory.

- 4. Insert the installation diskette labeled "HIgh C/C++ Sun" and "1 of *n*" (*n* may vary) into the diskette drive.

- 5. From the second window run the command:

cpio -ivB BSP\_hcppc.tar.Z < /dev/rfd0</pre>

where /dev/rfd0 is the name of your diskette device.

- 6. When the system prompts you for a new volume, move to the first window and type **eject** to eject the diskette. Insert the next diskette.

- 7. Move to the second window and type the name of the diskette drive (/dev/rfd0) to continue the process.

- 8. If prompted for more diskettes, repeat the previous two steps. When finished, type **eject** to remove the final diskette.

- 9. Return to the first window and verify that the following file is installed under the *lusr* directory:

#### BSP\_hcppc.tar.Z

10.Run the following command to unpack and install the files:

zcat BSP\_hcppc.tar.Z | tar xvf -

Installation for SunOS is complete. The tar.Z file may be removed to recover space.

#### Instructions for Solaris 2.4 (or higher) only:

- 1. Log in as root or use the su command to become the superuser.

- 2. Open at least two windows for this procedure.

- 3. Use the cd command to change to the /usr directory.

- 4. Insert the installation diskette labeled "HIgh C/C++ Sun" and "1 of *n*" (*n* may vary) into the diskette drive.

- 5. From the first window type **volcheck.** This creates a file called **/vol/dev/rdiskette0/unlabeled** (the diskette device name).

If the system pops up a message box saying the diskette format is unrecognized, ignore the message and cancel the message box. The name of the file created may be different on your system. You can use the **eject -q** command to see the actual name. The file name returned is the name that should be used in the subsequent steps.

6. From the second window run the command:

cpio -ivB BSP\_hcppc.tar.Z < /vol/dev/rdiskette0/unlabeled</pre>

where /voldev/rdiskette0/unlabeled is the name of your diskette device.

7. When the system prompts you for a new volume, move to the first window. Type **eject** if the system did not automatically eject the diskette. Insert the next diskette and type **volcheck**.

- 8. Move to the second window and type the name of the diskette drive (/vol/dev/rdiskette0/unlabeled) to continue the process.

- 9. If prompted for more diskettes, repeat the previous two steps. When finished, type **eject** to remove the final diskette.

10.Return to the first window and verify that the following file is installed under the *lusr* directory:

#### BSP\_hcppc.tar.Z

11.Run the following command to unpack and install the files:

zcat BSP\_hcppc.tar.Z | tar xvf -

Installation for Solaris is complete. The tar.Z file may be removed to recover space.

The IBM High C/C++ Compiler is installed in the **/usr/highcppc** directory tree. It may be necessary to change ownership of these directories, their subdirectories and their contents if other users require access to them. The **/usr/highcppc/bin** directory contains the files required for the IBM High C/C++ Compiler. Those files include:

- asppc Assembler for assembler language programs

- Idppc ELF linker/binder to build applications to be run on the board

- hcppc High C/C++ compiler for C programs

- arppc ELF library archiver

The **readme** file under the **/usr/highcppc** directory contains the latest information regarding the compiler and should be considered essential reading.

If you installed the compiler into a directory other than **/usr/highcppc**, edit the **bin/hcppc.cnf** file, and locate the line near the top of the file that reads **HCDIR=/usr/highcppc**. Change this to reflect the directory that the compiler was installed into. Save your changes and exit the editor.

## 3.2.3 RISCWatch Debugger Installation - Sun

Please refer to the *RISCWatch Debugger Installation Guide* for debugger installation instructions. Be sure to follow the instructions for Sun installation.

## 3.3 RS/6000 Software Installation

## 3.3.1 BSP Software Installation - RS/6000

Before beginning the installation, you must have:

- BSP for RS/6000 installation diskettes

- A RISC System/6000, running AIX Version 4.1 or higher

- Superuser privileges on the AIX system

#### The following procedure installs the BSP software support package.

- 1. Log in as **root** or use the AIX **su** command to become the superuser.

- 2. Use the cd command to change to the /usr directory.

- 3. Insert the installation diskette labeled "BSP RS6K" and "1 of n" (n may vary) into the diskette drive

4. Issue the following command:

tar -xvf /dev/rfd0

where /dev/rfd0 is the name of your diskette device

- 5. When the system prompts you for the next media, eject the diskette, insert the next diskette, and press **Enter**.

- 6. If prompted for more media, repeat the previous step for the remaining BSP diskettes. When finished, remove the final diskette from the diskette drive.

- 7. Verify that the following file is installed under the **/usr** directory:

#### BSP.tar.Z

8. Run the following command to unpack and install the files:

zcat BSP.tar.Z | tar xvf -

Installation for AIX is complete. The tar.Z file may be removed to recover space.

The BSP software is installed in the **/usr/osopen** directory tree. It may be necessary to change ownership of these directories, their subdirectories and their contents if other users require access to them.

The **/usr/osopen** directory tree contains the files and tools that support OS Open application and ROM development. The **/usr/osopen** subdirectories and their contents are as follows.

#### /bin

This directory contains several host based utilities used for application and ROM program development.

- elf2rom creates a ROM image from an ELF executable file

- eimgbld creates a ROM Monitor loadable image from an ELF executable file

- hbranch places an absolute branch in the last address of a ROM image

- rambuild creates an assembler source file that contains the files found in a specified directory

- trc41 post-processes OS Open trace snapshots for AIX 4.1

#### /examples

This directory contains example OS Open programs.

#### /m405\_evb

This directory contains the ROM Monitor and OS Open platform specific code for the reference board included in the kit.

- README.TXT contains the latest information regarding this release

- /include contains OS Open include files

- /Id contains dynamically loadable modules that can be run from OS Open's OpenShell

- /lib contains OS Open libraries

- /m4 contains assembler preprocessor include files

- /openbios contains the source code for the ROM Monitor (See Chapter 7, "ROM Monitor")

- /samples contains samples programs that can be compiled and run

Considerable effort goes into providing a quality product with consistent documentation. To insure that our customers have the advantage of the latest software features and updated information, **README.TXT** may contain clarifications and/or additional information and should be considered essential reading.

#### /COMMENT.USR and COMMENT.DOC

Please take the time to complete these user comment forms. Your feedback and suggestions will help us to improve our products and technical publications. FAX and e-mail instructions are included in each of the files.

## 3.3.2 High C/C++ Evaluation Compiler Installation - RS/6000

Before beginning the installation, you must have:

- High C/C++ for RS/6000 installation diskettes

- A RISC System/6000, running AIX Version 4.1 or higher

- Superuser privileges on the AIX system

#### The following procedure installs the High C/C++ compiler.

- 1. Log in as root or use the AIX su command to become the superuser.

- 2. Use the **cd** command to change to the **/usr** directory.

- 3. Insert the installation diskette labeled "High C/C++ RS6K" and "1 of *n*" (*n* may vary) into the diskette drive

- 4. Issue the following command:

tar -xvf /dev/rfd0

where /dev/rfd0 is the name of your diskette device

- 5. When the system prompts you for the next media, eject the diskette, insert the next diskette, and press **Enter**.

- 6. If prompted for more media, repeat the previous step for the remaining High C/C++ diskettes. When finished, remove the final diskette from the diskette drive.

- 7. Verify that the following file is installed under the **/usr** directory:

#### BSP\_hcppc.tar.Z

8. Run the following command to unpack and install the files:

zcat BSP\_hcppc.tar.Z | tar xvf -

Installation for AIX is complete. The tar.Z file may be removed to recover space.

The IBM High C/C++ Compiler is installed in the **/usr/highcppc** directory tree. It may be necessary to change ownership of these directories, their subdirectories and their contents if other users require access to them. The **/usr/highcppc/bin** directory contains the files required for the IBM High C/C++ Compiler. Those files include:

- **asppc** assembler for assembler language programs

- **Idppc** ELF linker/binder to build applications to be run on the board

- hcppc High C/C++ compiler for C programs

- **arppc** ELF library archiver

The readme file under the **/usr/highcppc** directory contains the latest information regarding the compiler and should be considered essential reading.

If you installed the compiler into a directory other than **/usr/highcppc**, edit the **bin/hcppc.cnf** file, and locate the line near the top of the file that reads **HCDIR=/usr/highcppc**. Change this to reflect the directory that the compiler was installed into. Save your changes and exit the editor.

## 3.3.3 RISCWatch Debugger Installation - RS/6000

Please refer to the *RISCWatch Debugger Installation Guide* for debugger installation instructions. Be sure to follow the instructions for RS/6000 installation.

# Chapter 4. Host Configuration

Several host configuration steps are required to facilitate communications between the host computer and the board. These steps are outlined in this chapter. Please refer to the section corresponding to your host system.

# 4.1 PC Host Configuration

The following sections discuss setup of host configuration for PC hosts.

# 4.1.1 Serial Port Setup - PC

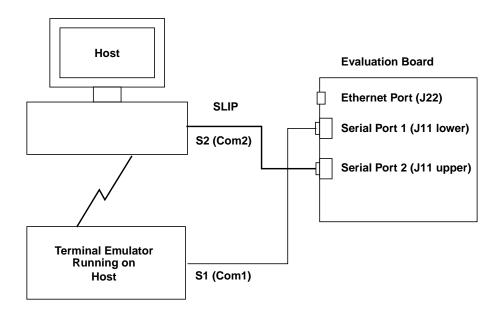

Most PCs include two serial ports to support communications via asynchronous data transfer. These ports are sometimes referred to as communication or COM ports. These ports are usually accessed from the back of the system unit. You should consult your PC literature to determine how many serial ports are available on your unit and where they are located. In this section, S1 and S2 refer to the respective serial ports on the host PC, and SP1 and SP2 to the respective serial ports on the board.

When properly configured, one serial port can be used to connect a terminal emulator running on the host to the ROM Monitor running on the board, and the other to provide a Serial Line Internet Protocol (or SLIP) network interface between the host and the board to download and debug applications. The SLIP host-to-board connection is optional if the recommended Ethernet connection is going to be used for host-to-board communications. This section addresses the proper configuration of the S1 and S2 serial ports to support these connections. Users should also refer to the Windows on-line help for "Changing Serial Port Settings".

The connection of the terminal emulator running on the host to the ROM Monitor running on the board, is made through the S1 serial port on the PC and the SP1 (J11 lower) serial port on the board. The S1 port must be configured for a baud rate of 9600, 8 data bits, 1 stop bit, and no parity. The proper setting of these parameters is discussed later in the section on terminal emulation.

A connection between the S2 serial port on the host and the SP2 (J11 upper) serial port on the board, provides a SLIP network interface to download and debug application programs from the host. This connection can be used in place of the recommended Ethernet connection.

**Note:** Windows users who want to establish a SLIP host-to-board connection over a second serial port, require additional software since the TCP/IP package that comes with Windows does not support SLIP communications. Trumpet Winsock is one package that supports the SLIP protocol. Trumpet is *not* recommended for Windows users already connected to a network since installing Trumpet may cause problems with previously defined networks. If the recommended Ethernet host-to-board connection is going to be used (instead of a SLIP host-to-board connection), Windows users do not need to install Trumpet since the TCP/IP package that comes with Windows can be used to establish the Ethernet connection.

To establish a SLIP network over the S2 serial port for host-to-board communications, define a SLIP interface via the TCP/IP package being used. Since TCP/IP packages for PCs vary, users should consult their TCP/IP literature or their system administrator on how to establish the SLIP interface between the host and the board. The following IP addresses are suggested for the SLIP interface:

- PC host (source): *8.1.1.4*

- Board (destination): 8.1.1.5

Make a note of the IP addresses selected since they will be needed later.

Trumpet Winsock users can use the following steps as a guide to establishing the SLIP interface:

- 1. Open the Trumpet Winsock by double clicking on the Trumpet Winsock icon in the Trumpet Winsock Files program group.

- 2. If setup was bypassed during installation, your connection should fail. A Trumpet Winsock window comes up indicating your connection status. Select Setup from the File menu to open the Setup dialog.

- 3. Set the IP address field to the IP address of the PC host: *8.1.1.4* is suggested to maintain consistency with this document.

- 4. Select SLIP under Drivers and then go to Dialler settings.

- 5. Select the appropriate COMM port (COM2 for example) to be used for SLIP communications.

- 6. Set the Baud rate to 38400.

- 7. Disable Hardware handshaking and make sure No automatic login is selected. Use the default settings for the remaining options and/or check the help for more details.

- 8. Select **OK** from Dialler Settings and then **OK** from Setup.

- 9. Edit the **hosts** file found in the installed Trumpet directory to include both the PC host IP address and the board IP address. For example:

- 8.1.1.4 local\_slip

- *8.1.1.5* board\_slip

After entering all the information, you may need to restart Trumpet Winsock for the network setup to take effect.

Prior to exiting Windows, we recommend terminating Trumpet Winsock (close the application). If you do not follow this recommendation, subsequent Trumpet starts may fail. If this occurs, you will need to reboot your system.

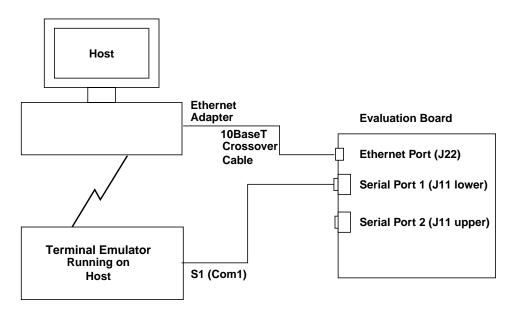

#### 4.1.2 Ethernet Setup - PC

In addition to (or in place of) the SLIP connection, an Ethernet connection can be used for host-toboard communications. The Ethernet connection is made through an Ethernet adapter on the host and the 10BaseT/100BaseTX Ethernet port (J22) on the board. Ethernet is much faster than SLIP and is recommended when downloading large applications on to the board or when using the RISCWatch debugger.

An Ethernet connection may require additional hardware. The reference board supports a standard Ethernet, twisted pair (10BaseT/100BaseTX) connection. This connection requires that the host PC be equipped with an appropriate Ethernet adapter. The host adapter is not included in the kit. Please consult your PC and adapter documentation for requirements and installation instructions.

At a minimum, a 10BaseT/100BaseTX connection requires a crossover Ethernet twisted pair cable (included in the kit) for point-to-point communications. The Ethernet crossover cable is for 10Mb/s direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. If

you want more than two nodes, or 100Mb/s connectivity, you will need a hub and straight-through twisted pair cables.

Other hardware required will depend on the type of Ethernet adapter you have on your PC and whether the board is being connected to an existing Ethernet network. Please consult your system administrator and the documentation included with the adapter hardware for additional instructions.

Establishment of an Ethernet interface requires a host IP address. If the host PC is connected to an existing Ethernet network, the host IP address should already be defined and there is no need to set it again. Consult your network administrator on how to obtain the host's Ethernet IP address and how to add the board to the existing network.

To set the host IP address for the Ethernet connection:

- 1. Select the My Computer icon from the desktop.

- 2. Select Control Panel.

- 3. Select Network.

- 4. Add the appropriate Adapter network component for the Ethernet adapter being used (if not already added).

- 5. Add a Protocol network component of Microsoft TCP/IP' (if not already added). Specify the IP address (7.1.1.4 is recommended to maintain consistency with this document) and netmask (255.255.240.0) to be used.

For the update to take effect, TCP/IP may need to be restarted. This may require a reboot of the system and/or a restart of TCP/IP. Make a note of the host IP address assigned to the Ethernet adapter, as this value will need to be made known to the ROM Monitor on the board.

#### 4.1.3 ROM Monitor-Debugger Communication Setup - PC

Before the RISCWatch Debugger can be used, some additional steps need to be taken to establish ROM Monitor-Debugger communications. These steps involve an update of the TCP/IP **services** file to establish a named communications port and port number for TCP/IP socket communications, and a restart of the TCP/IP package for the update to take effect.

Windows 95/98 places the **services** file under C:\WINDOWS\SERVICES. Windows NT places the **services** file under C:WINDOWS\SYSTEM32\DRIVERS\SERVICES. Users should consult their TCP/IP documentation or system administrator if they can not locate the file. The following lines must be added to the file:

| osopen-dbg | 20044/tcp | # | for | RISCWatch | OS  | Open  | debug |

|------------|-----------|---|-----|-----------|-----|-------|-------|

| osopen-dbg | 20044/udp | # | for | RISCWatch | ror | n_mon | debug |

For the update to take effect, TCP/IP needs to be restarted. This might require a reboot of the system and a restart of the TCP/IP package.

# 4.2 Sun Host Configuration

Sun configuration requires that you be the superuser of the host workstation. This is accomplished by logging in as **root** or by using the **su** command to become the superuser.

# 4.2.1 Serial Port Setup - SUN

The Sun workstation includes two serial ports to support communications via asynchronous data transfer. These ports are labeled Serial A and Serial B on the back of the Sun's system unit. Some SPARCstation models multiplex these two ports into one physical port labeled A/B (use A if it's available since use of the B port requires a special de-multiplexing cable from Sun). This section refers to these ports as S1 and S2, respectively. When properly configured, one of the serial ports can be used to connect a terminal emulator running on the host to the ROM Monitor running on the board. This connection is made through the S1 serial port on the Sun and the SP1 (J11 lower) serial port on the board.

The S1 port on the host must be configured for a baud rate of 9600, 8 data bits, 1 stop bit, and no parity. The proper setting of these parameters is discussed later in the section on terminal emulation.

# 4.2.2 Ethernet Setup - SUN

Since all Sun SPARCstations come equipped with an Ethernet (or AUI) port, an Ethernet connection is used for host-to-board communications. The reference board supports a Standard Ethernet, twisted pair (10BaseT/100BaseTX) connection. An Ethernet connection may require additional hardware.

At a minimum, a 10BaseT/100BaseTX connection requires a crossover Ethernet twisted pair cable (included in the kit) for point-to-point communications. The Ethernet crossover cable is for 10Mb/s direct connection to a single host and *cannot* be used with a hub or a building's Ethernet network. If you want more than two nodes, or 100Mb/s connectivity, you will need a hub and straight-through twisted pair cables.

Establishment of an Ethernet interface requires a host IP address. If the host SPARCstation is connected to an existing Ethernet network, the host IP address should already be defined. Consult your network administrator on how to obtain the host's Ethernet IP address and how to add the board to the existing network.

If the host SPARCstation is not connected to an existing Ethernet network, then a network between the board and the host must be established. The **ifconfig** command can be used to establish such a network. Users should consult their network administrator and Sun documentation for additional information. A host IP address of *7.1.1.4* is suggested to maintain consistency with this document.

Make a note of the host's IP address since it will need to be made known to the ROM Monitor on the board.

# 4.2.3 ROM Monitor-Debugger Communication Setup - SUN

Before the RISCWatch Debugger can be used, the TCP/IP **services** file must be updated to allow ROM Monitor-Debugger communications.

To modify the *letc/services* file, you need to log in as **root** or the superuser (**su**). The following lines must be added to the file:

| osopen-dbg | 20044/tcp | # | for | RISCWatch | OS  | Open  | debug |

|------------|-----------|---|-----|-----------|-----|-------|-------|

| osopen-dbg | 20044/udp | # | for | RISCWatch | ror | n_mon | debug |

# 4.3 RS/6000 Host Configuration

RS/6000 configuration requires that you be the superuser of the host workstation. This is accomplished by logging in as **root** or by using the AIX **su** command to become the superuser.

# 4.3.1 Serial Port Setup - RS/6000

The RS/6000 includes two serial ports to support communications via asynchronous data transfer. These ports are labeled S1 and S2 on the back of the RS/6000's system unit. When properly configured, one serial port can be used to connect a terminal emulator running on the host to the ROM Monitor running on the board, and the other to provide a Serial Line Internet Protocol (or SLIP) network interface between the host and the board to download and debug applications. This section addresses the proper configuration of the S1 and S2 serial ports to support these connections. Details on setting up the terminal emulator are discussed in a later chapter. In this section, S1 and S2 refer to the respective serial ports on the host RS/6000, and SP1 and SP2 to the respective serial ports on the board.

The connection of the terminal emulator running on the host to the ROM Monitor running on the board, is made through the S1 serial port on the RS/6000 and the SP1 (J11 lower) serial port on the board. A connection between the S2 serial port on the host and the SP2 (J11 upper) serial port on the board, provides a SLIP network interface to download and debug application programs on the board. If the recommended Ethernet connection is going to be used, the S2-to-SP2 SLIP connection is optional and does not need to be established.

Proper setup involves the configuration of **tty** devices for both the S1 and S2 serial ports on the host. **tty0** is used for the terminal emulator-to-ROM Monitor connection and **tty1** for the host-to-board SLIP connection. It is also necessary to establish a SLIP network interface between S2 on the host and SP2 on the board. The following steps should be taken to insure proper S1, S2 configuration:

- 1. Log in as **root** or the superuser (**su**).

- 2. Determine if the tty0, tty1 devices already exist.

- a. Enter smit

- b. Select Devices

- c. Select TTY

- d. Select List All Defined TTYs

Perform step 3 for each tty not listed.

Perform step 4 for each tty listed to insure that it is properly configured.

- 3. To add a tty device:

- a. Return to the TTY screen.

- b. Select Add a TTY.

- c. Select tty rs232 Asynchronous Terminal.

- d. Select sa0 Serial Port 1 (for ROM Monitor connection) when adding tty0.OR sa1 Serial Port 2 (for board SLIP connection) when adding tty1.

- e. Select **s1** for the port number when adding **tty0**.

- OR **s2** for the port number when adding **tty1**.

- f. Ensure that the BAUD rate is **9600** when adding **tty0**.

OR that the BAUD rate is **38400** when adding **tty1**.

- g. Ensure that the PARITY is **none**.

- h. Ensure that the BITS per character is 8.

- i. Ensure that the Number of STOP BITS is 1.

- j. Ensure that Enable LOGIN is **disabled**.

The default settings for all the other fields are satisfactory.

k. Select Do or press Enter.