# "Book E": An Enhanced PowerPC Architecture

Thomas Sartorius IBM Microelectronics Embedded PowerPC Principal Architect Pete Wilson Motorola Semiconductor Products Sector Senior Member of the Technical Staff

#### Presented by: Thomas Sartorius

All information in these materials is subject to change without notice. All information is provided on an "as is" basis, without any warranty of any kind.

### What is "Book E"?

Book E is the project name for the collaborative effort between Motorola and IBM to enhance the PowerPC Architecture<sup>™</sup>

Book E is a complete architectural definition, not just an addendum to the PowerPC Architecture

# Why are Motorola and IBM defining Book E?

### The marketplace is moving to applicationspecific systems with diverse needs

### Book E objectives:

- Provide an enhanced architecture definition with 64-bit capabilities

- Increase architectural flexibility

- Deliver optimizations specific to embedded systems

# Why are Motorola and IBM defining Book E?

#### PowerPC

Customers have identified the need to maintain the PowerPC Architecture, now and into the future

#### Book E objectives:

- Eliminate non-substantive architectural differences in future IBM and Motorola embedded PowerPC implementations

- Provide compatibility for existing PowerPC applications

### PswerPC

# **Complete 64-bit architecture**

- 64-bit addressing required for high-performance apps (e.g. RAID, networking, telecom)

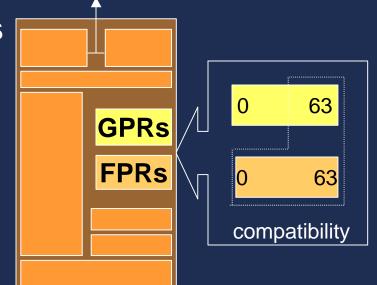

- 64-bit Book E processors can execute 32- and 64-bit applications

- Supports 32-bit legacy code

- Book E allows 32-bit or 64-bit processor implementations

- Optimize cost and performance for diverse system requirements

# Unified 32-/64-bit architecture, without modes

- Existing load/store/branch instructions calculate 32-bit addresses

- Existing arithmetic instructions produce 32- and 64-bit results

- 84 new instructions for 64-bit addressing and extended arithmetic

- Unified 32-/64-bit MMU

- Single MMU covers both 32- and 64-bit address translation

- Easier OS migration

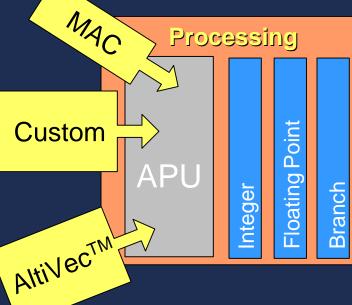

# Powerful capability to implement *pewerPC* custom functionality

- Book E allows Application-Specific Processing Units (APU) for instruction set extensions

- Single instruction stream

- Examples:

- DSP

- Multimedia

- Custom (e.g. Servo, print engine, automotive control)

#### • An APU design can be:

- Simple, sharing use of GPR file

- Complex, separate AP register file with direct load/store access

MOTOROLA

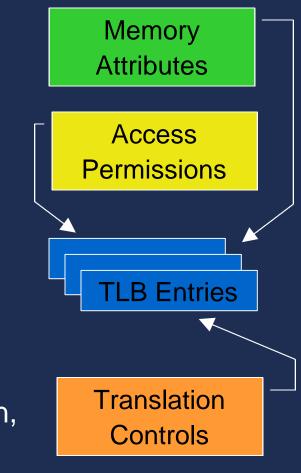

# Adaptable memory management **percerPC** for diverse operating environments

#### Architected software-managed TLB

- Architecture defines TLB functions

- System defines page table size, location, organization, supported page sizes, and TLB replacement strategy

#### Variable page sizes, 1KB to 1TB

- More efficient memory allocation

- Compact TLB can map large memory

#### Memory attributes

- Cache policy

- Endianness

- User-definable (e.g., code compression, memory hierarchy control, etc.)

MOTOROLA

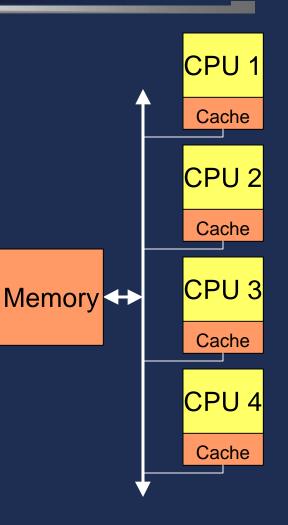

# High-performance memory architecture

#### Maintains PowerPC memory model

- Weakly-ordered memory access

- Full MP cache coherent architecture

- Implementation freedoms remain

- Improved memory barrier mechanisms

- Speeds lock management

- Benefits heavily multi-threaded apps like Java

- Support for cache locking

- Architected exception types and vectors for lock-related errors

# Two interrupt priority levels for real-time systems

# PC Crifical CSRR0 SRR0 CSRR1 SRR1 POPLCI1: critica **MSR**

#### Critical interrupt level for critical input, debug, watchdog

- Low latency response to highpriority devices

- Robust software debug of noncritical handlers

- Improved system reliability

- Non-critical interrupt level for TLB miss, memory protection, illegal op-codes, etc.

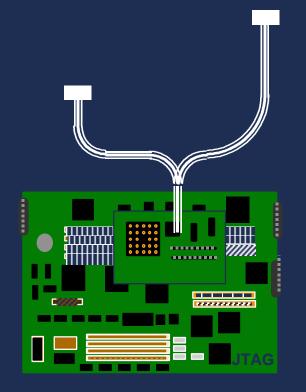

# Robust debug for highperformance systems

#### PSwerPC

#### Architected debug framework for application developers and tool vendors

- Instruction address compare

- Exact match, address bit mask, inclusive/exclusive ranges

- Data address compare

- Including data value compare

- Other debug events

- Instruction discontinuity, single step, asynchronous

- Architecture permits subset of debug facilities

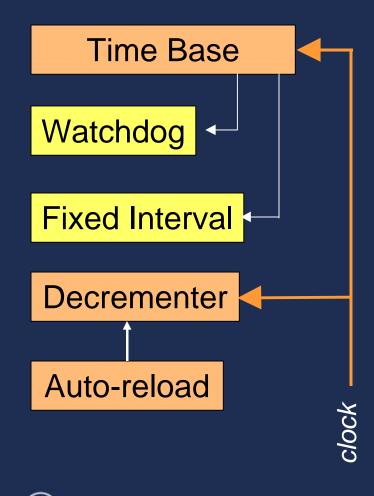

# Expanded timer facilities for hard real-time constraints

### PowerPC

- 64-bit time base register, for general system time maintenance

- Improved 32-bit decrementer

- Auto-reload and auto-stop modes

- SW timer for multitasking

- Fixed interval timer, for periodic system maintenance

Watchdog timer, for system error recovery

## PewerPE

# **Architectural compatibility**

- Backward and forward compatibility with existing PowerPC implementations

- Previous PowerPC 32-bit application binaries will run unmodified on new Book E implementations

- New Book E 32-bit application binaries will run unmodified on previous PowerPC implementations

- Improvements for system software

- Significant enhancements for RTOS memory management

- More robust interrupt handling

- Consistent architecture for application and tool developers

### PewerPC

# **Commitment to Book E**

#### Motorola and IBM:

- Have jointly defined the Book E enhanced PowerPC Architecture

- Will continue to collaborate to enhance the architecture

- Will independently develop products based on the Book E architecture

- Each have the ability to sub-license the architecture

#### The Book E specification is available today at:

- http://motorola.com/PowerPC

- http://www.chips.ibm.com/products/powerpc

## PewerPE

## Summary

- Book E provides enhancements to address future marketplace requirements, while maintaining support for existing PowerPC-based systems

- Book E provides flexibility for application-specific optimizations while providing architectural consistency for software development

- IBM and Motorola are making Book E a premier architecture for high-performance and cost-effective applications

Motorola and the Motorola logo are registered trademarks, and AltiVec Technology and the AltiVec Technology logo are trademarks of Motorola, Inc. IBM, the IBM logo, PowerPC, the PowerPC logo and PowerPC Architecture are trademarks of International Business Machines Corporation